近日��,中國科大微電子學院龍世兵教授課題組的五篇論文入選第36屆功率半導體器件和集成電路國際會議(IEEE International Symposium on Power Semiconductor Devices and ICs���,簡稱IEEE ISPSD)報告����。IEEE ISPSD是功率器件領域最具影響力和規模最大的頂級國際學術會議����,被認為是功率半導體器件和集成電路領域的奧林匹克會議�,IEEE ISPSD 2024于今年6月2日至6月6日在德國舉辦。中國科大微電子學院鄭柘煬特任教授和徐光偉特任研究員帶隊參加此次盛會。

圖1.參會人員合照:鄭柘煬教授(右二)���,徐光偉研究員(右一)。

本次入選的五篇論文工作如下:

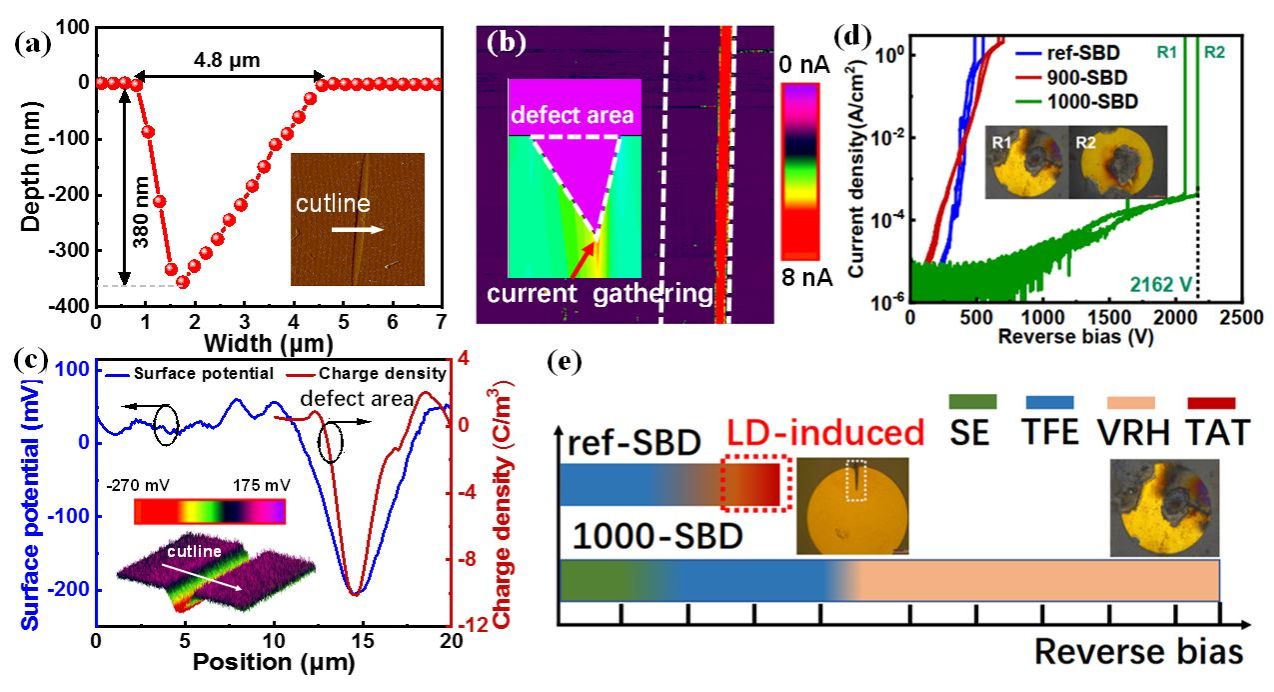

1.氧化鎵關鍵缺陷識別和抑制方法

為了制備高耐壓氧化鎵肖特基勢壘二極管(SBD)�����,發揮氧化鎵材料的優勢��,高性能的功率二極管需要在襯底上外延生長低摻雜濃度的外延層作為承壓區域����。鹵化物氣相外延(HVPE)的方法結合了生長速度��,晶體質量等優勢��,該方法成為了氧化鎵外延生長的重要方式。但是由于生長速度過快,在生長過程中晶體內部容易產生部分無序或者孔洞,這些缺陷可能會對器件性能造成巨大影響。在這項工作中��,通過微光顯微鏡(EMMI)的方式���,識別了一種沿著(010)晶向的線型晶格缺陷為一種導致氧化鎵SBD提前擊穿的關鍵缺陷(圖2)��。通過開爾文探針及原子力探針的表征方式�����,揭示了該缺陷區域的電學特性:固定負電荷的聚集導致電場增大,從而造成漏電增大和提前擊穿。此外�����,研究提出了通過高溫氧氣退火的方式����,成功修復了該缺陷,減少了晶圓上缺陷的數目,并成功制備了高擊穿氧化鎵SBD��。研究成果以“The Role of Line-shaped Defects in Premature Breakdown ofβ-Ga2O3Power Diode and Suppression by Oxygen Annealing”為題作為發表在IEEE ISPSD 2024上并作現場匯報����,第一作者為博士生劉金楊。

圖2.(a-c)線型缺陷的表面形貌及電學特性,(d)通過氧氣退火改善缺陷后的器件擊穿特性�,(e)優化前后器件的漏電機制對比�。

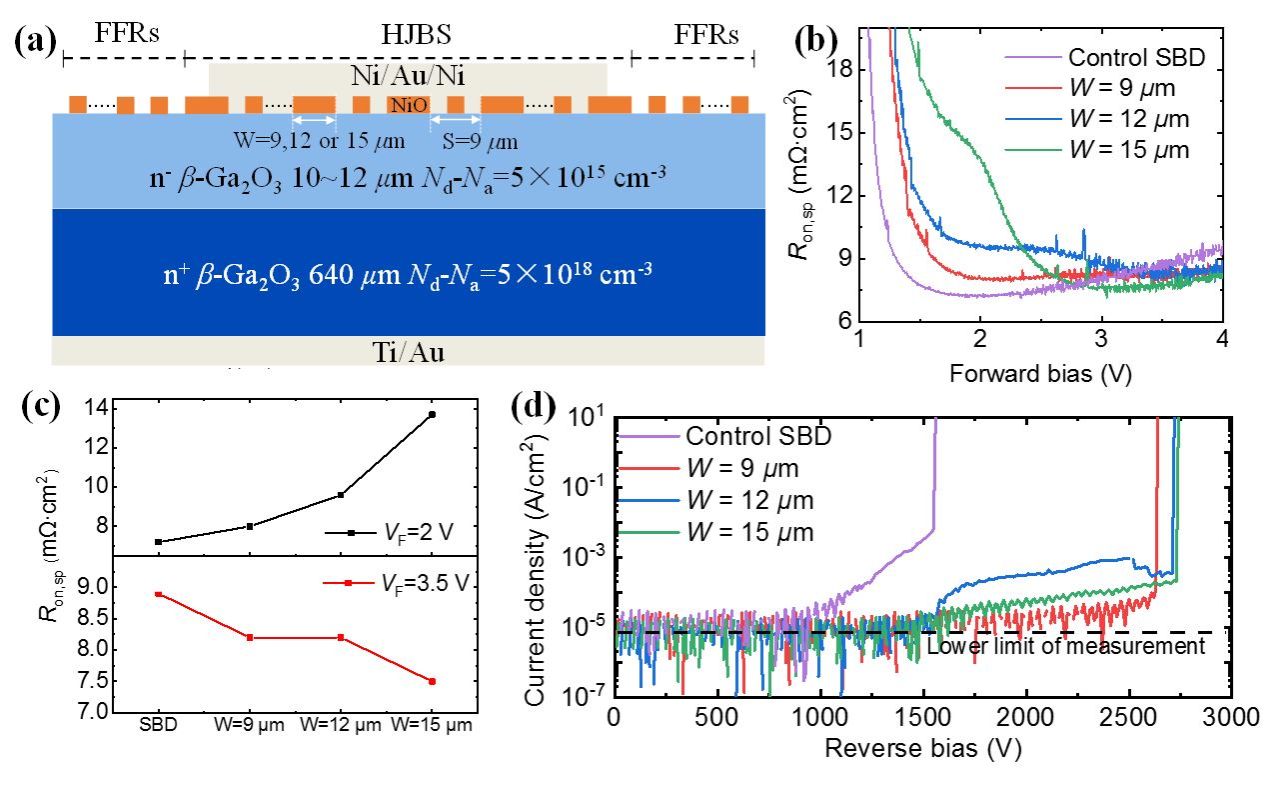

2.低漏電�、高耐壓的β-Ga2O3異質結勢壘肖特基二極管

針對高電場下β-Ga2O3SBD器件肖特基結中心區域仍會引起較大的泄漏電流這一問題,引入了降低表面電場(RESURF)技術—結勢壘肖特基結構。p-NiO被嵌入到肖特基中心表面以形成p-n結交替排列的β-Ga2O3HJBSD器件����。得益于較強的RESURF效應�,β-Ga2O3HJBSD器件表現出小于1 mA/cm2的極低的反向泄漏電流��,并且擊穿電壓達到了2.7 kV以上����。該β-Ga2O3HJBSD器件成功結合了SBD和HJD器件優勢���,兼具了低開啟電壓�、低泄漏電流和高擊穿電壓的優異特性(圖3)。研究成果以“2.7 kVβ-Ga2O3Heterojunction Barrier Schottky Diode with Low Leakage Current < 1 mA/cm2Based upon RESURF Effect”為題發表在IEEE ISPSD 2024上,第一作者為博士生郝偉兵。

圖3. (a)垂直氧化鎵HJBSD器件結構示意圖,(b)提取SBD和HJBSDs器件的比導通電阻�����,(c)分別在正向導通電壓2V(異質結導通之前)和3.5V(異質結導通之后)下提取SBD和HJBSDs的導通電阻�����,(d)SBD和HJBSDs器件的反向擊穿特性對比��。

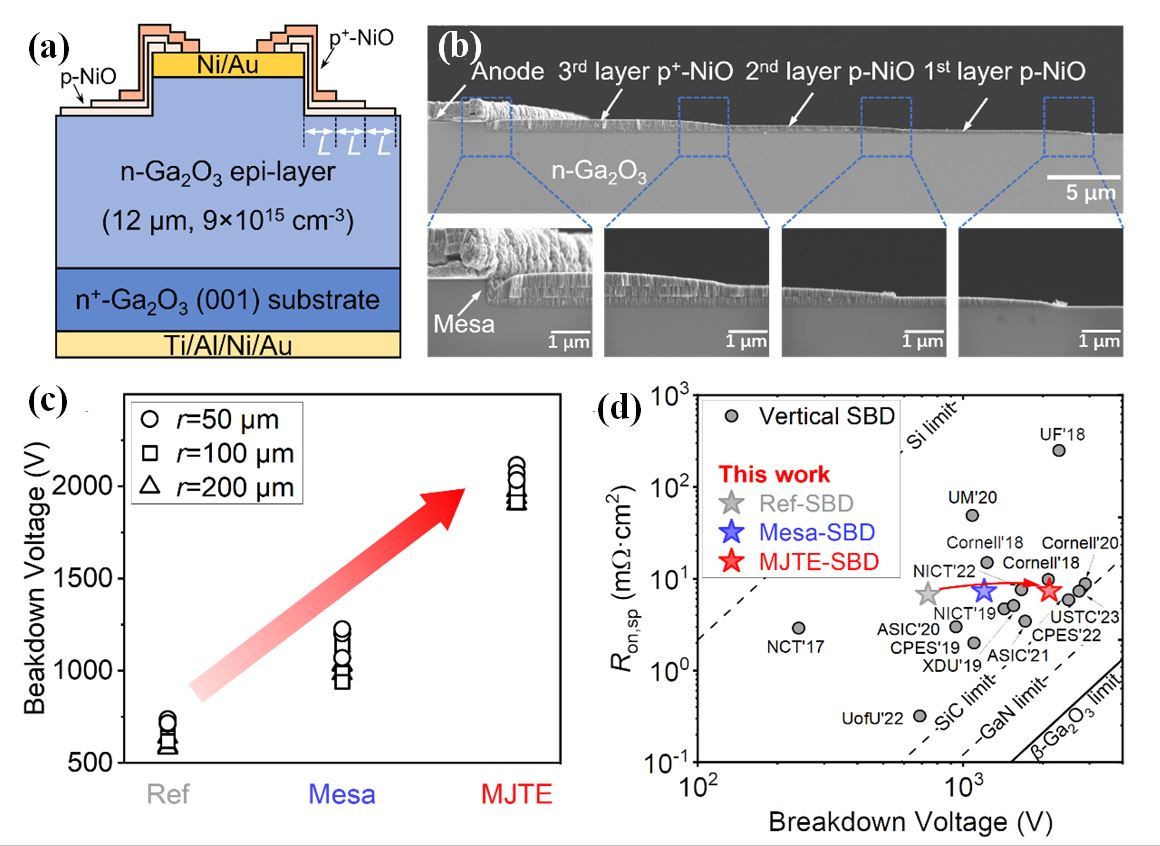

3.高耐壓氧化鎵肖特基勢壘二極管研究

近年來�,基于β-Ga2O3的肖特基勢壘二極管(SBD)研究迅速發展,并有望率先實現商業化�。然而�����,目前器件的實際性能與理論極限尚有較大差距,有效的邊緣終端設計對于提升器件性能至關重要���。臺面終端(Mesa)能夠有效地將SBD邊緣柱面結或球面結去除,使得整個器件呈現比較均勻的電場分布�。然而�,高電場在蝕刻臺面側壁的分布���,以及干法刻蝕引起的表面電荷富集�,可能存在額外泄漏電流和提前擊穿的風險?����;诖?���,課題組設計并制備了具有復合終端的高性能β-Ga2O3SBD(圖4)。該復合終端(MJTE)將臺面終端和漸變結終端拓展結構(JTE)相結合����。臺面設計避免了陽極邊緣的峰值電場�����,而漸變多層P型氧化鎳(NiO)的設計進一步有效調節了電場分布的梯度。通過TCAD仿真工具���,該工作系統研究了電場分布與NiO厚度、臺面深度和JTE長度之間的關系���。結合優化參數�,實際制備器件的擊穿電壓從738 V提升到2116 V,功率優值(PFOM)提高了七倍(從81.05到608.35 MW/cm2)�。這項工作為提高β-Ga2O3SBD的性能提供了切實有效的解決方案����。研究成果以“Improvedβ-Ga2O3Schottky Barrier Diodes Featuring p-NiO Gradual Junction Termination Extension within Mesa Structure”為題發表在IEEE ISPSD 2024上�,第一作者為博士生韓照。

圖4.(a)設計的β-Ga2O3MJTE-SBD器件結構示意圖,(b)制備器件的掃描電子顯微鏡圖像,(c)器件擊穿特性統計分布結果����,(d)該工作器件與國際已報道器件的性能對比�。

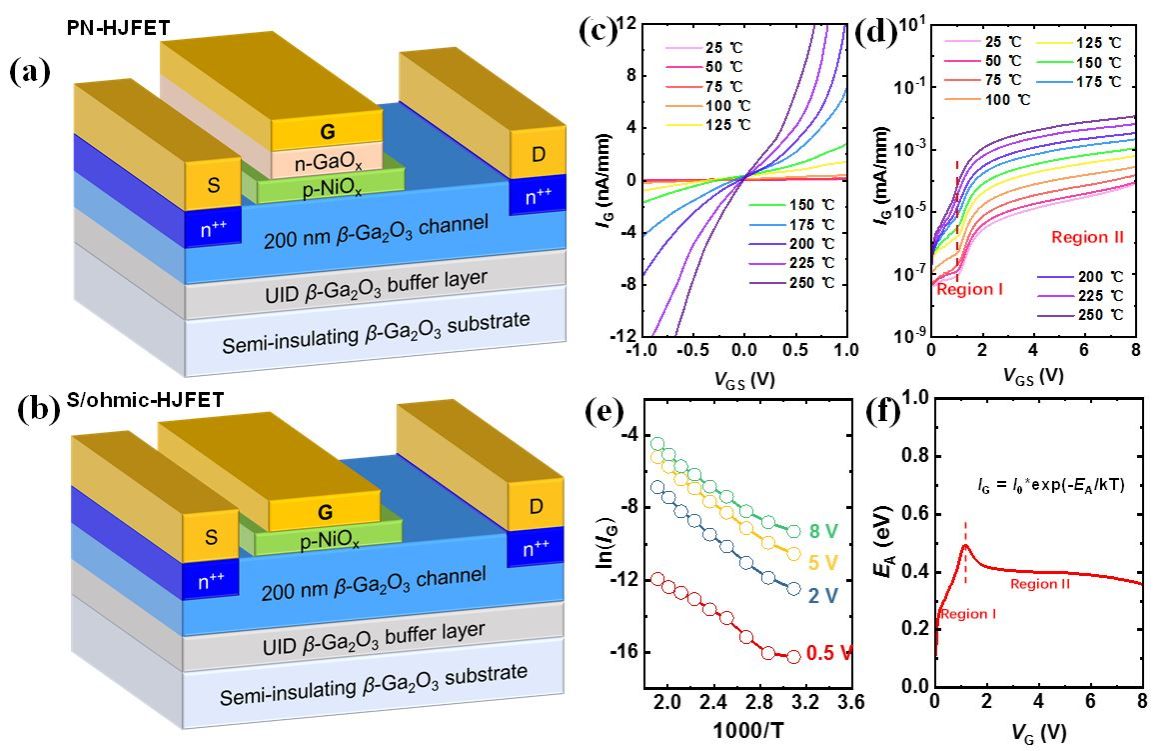

4.低柵漏電氧化鎵pn結-異質結場效應晶體管

基于p-NiO的β-Ga2O3異質結場效應晶體管在高功率和高頻開關應用中顯示出巨大潛力。然而在先前的研究中����,基于p-NiO的β-Ga2O3異質結場效應晶體管存在寄生的柵源pn二極管�,導致較大的柵極漏電電流�����,促使需要創新的解決方案��。該工作中,針對β-Ga2O3異質結場效應晶體管(HJFET)的柵極擊穿問題��,通過引入NiOx/GaOx柵極堆疊結構�,成功設計并制備了一種新型的pn結-異質結場效應晶體管PNJ-HJFET。這種結構顯著提高了柵極擊穿電壓至14.2 V�����。PNJ-HJFET在25至250 ℃的寬溫度范圍內����,表現出了優異的穩定性和極低的閾值電壓偏移(圖5)。此外�����,通過分析柵極漏電特性��,揭示了PNJ-HJFET在不同溫度下的導電機制,為β-Ga2O3HJFETs的柵極擊穿問題提供了一種有效的解決方案。研究成果以“Enhanced Gate Breakdown inβ-Ga2O3HJFET through a NiOx/GaOxp-n Junction Gate Stack”為題發表在IEEE ISPSD 2024上,第一作者為博士后周選擇����。

圖5.(a)氧化鎵PN-HJFET器件和(b)氧化鎵S/ohmic-HJFET器件結構示意圖��,(c)PN-HJFET器件的柵極電流-電壓(IG-VG)特性,(d)在溫度范圍25-250℃下測量的PN-HJFET器件的柵極電流-電壓特性,(e)IG-1000/T的Arrhenius曲線��,(f)從圖(e)提取的激活能EA���。

5.千伏級氮離子注入氧化鎵垂直晶體管

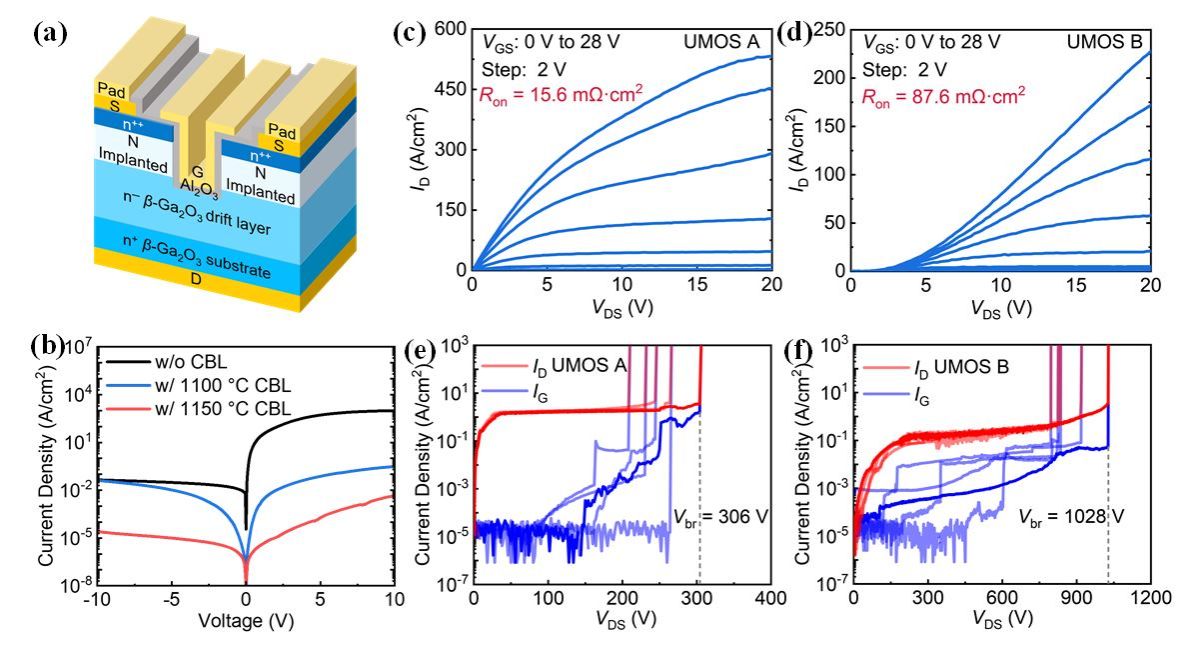

由于p型氧化鎵的實現極具挑戰��,這在一定程度上限制了氧化鎵增強型晶體管的實現方案����。而受主摻雜可補償氧化鎵中的載流子�,在氧化鎵材料中實現電流阻擋層,這為實現增強型場效應晶體管提供了新的思路。氧化鎵中形成電流阻擋層的主流方法包括氧氣氛圍高溫退火�����、鎂元素摻雜及氮元素摻雜��。但在目前的研究中���,電流阻擋層的漏電特性仍不理想���,導致器件在關斷狀態下泄漏電流較高��,容易造成器件的提前擊穿。該工作采用氮離子注入的方法實現了電流阻擋層,并通過優化離子注入后的退火激活溫度抑制了電流阻擋層的漏電����。基于優化后的離子注入后退火工藝����,該工作實現了擊穿電壓高于1 kV的U型槽柵垂直晶體管��,與優化前的器件相比,其擊穿電壓有顯著提高�,初步展示了基于電流阻擋層的氧化鎵垂直晶體管的潛力��,如圖6所示。研究成果以“1-kVβ-Ga2O3UMOSFET with Quasi-Inversion Nitrogen-Ion-Implanted Channel”為題發表在IEEE ISPSD 2024上����,并獲得大會唯一最佳海報獎(Best Poster Award)���,見圖7�����,博士生劉琦和博士后周選擇為該論文共同第一作者����。

圖6.(a)β-Ga2O3UMOSFET器件結構示意圖����,(b)不帶電流阻擋層(CBL)和分別在1100℃、1150℃下退火的帶CBL的測試結構的電流-電壓特性,(c)UMOS A(1100℃退火)和(d)UMOSB(1150℃退火)器件的脈沖輸出特性,(e)UMOS A(1100℃退火)和(f)UMOSB(1150℃退火)器件的擊穿特性。

圖7. 我校博士生劉琦獲獎(最佳海報獎)頒獎現場����。

以上五項研究成果得到了國家自然科學基金����、中國科學院�����、科技委、廣東省重點領域研究發展計劃�����、中國科學技術大學青年創新重點項目的資助����,同時得到了中國科學技術大學微納研究與制造中心、信息科學實驗中心的支持�����。

(微電子學院)